# Temperature analysis of L-Shaped and U-Shaped Tunnel Field Effect Transistors: Comparative Study

### Sweta Chander and Sanjeet Kumar Sinha

School of Electronics & Electrical Engineering Lovely Professional university, Phagwara, Punjab, India

E-mail: sweta.25028@lpu.co.in

Abstract— This paper investigated the comparative study of L-shaped Tunnel Field Effect Transistors (TFETs) and U-shaped TFETs. The effect of temperature has been studied for both device characteristics in terms of surface potential, electric field, and transfer characteristics. The ON current, as well as OFF current of L-shaped and U-shaped TFETs structure, shows the enhanced performance due to large area of channel length. The addition of n-type pocket under the source enhances the ON current and OFF current of both the devices. L-shaped and U-shaped TFETs structure, both, are easy to fabricate and cost-effective due to the use of already established Si technology. In next-generation devices, the superior performance of L-shaped and U-shaped TFETs structure makes them a promising contender for low power applications. All the simulation has been d done using Atlas Silvaco TCAD software.

# I. INTRODUCTION

For next-generation integrated circuits, Tunnel Field Effect Transistors (TFETs) act as promising successors of MOS devices [1]-[5].In MOS devices, the subthreshold swing (SS) cannot lower than 60 mV/dec due to thermionic emission transportation of charge carrier which becomes the limitation of MOS transistors [6]-[7]. TFETs could achieve SS less than 60 mV/decade by using band-to-band tunnelling (BTBT) at room temperature. The lower SS of TFET makes the device suitable for low power applications. This advantage of TFET makes it a popular alternative device but it is very hard to utilize in real-world applications. The inherent property of TFET due to asymmetric drain and source structure, which brings problems in circuit-level designing. Unlike MOS transistors, TFETs is unidirectional current path because of asymmetric source/drain design. Some researchers studied TFET and gave the theoretical prediction that it suffers from low ON current and high SS due to lower BTBT rates [8]-[9].

In addition, BTBT between the drain region and channel region enhancesthe OFF current of TFET due to increases in ambipolarity. Many researchers have been studied various

Page | 2884 Copyright @ 2019Authors

techniqueslike-new device structure [10]-[12] to overcome the disadvantages of TFETs [13]-[17] ,like-new device design such as new device structures and heterojunction to improve the ON current. To get large BTBT, Ref [18] reported an L-shaped TFET with mesa-shaped p-type source and intrinsic Si is situated between the source region and gate dielectrics. However, L-shaped TFET gives high ON current and low SS then also there are issues of hump characteristics that gives enhancement in OFF current and decrease SS of the device [19]. The U-shaped TFETs with SiGe as the source is reported in [20] to increase the ON current, get small SS and decrease OFF current.

In this work, L-shaped and U-shaped TFETs are compared in terms of surface potential, electric field, and transfer characteristics. The variation of temperature has been done to analyze different parameters for U-shaped and L-shaped devices. The addition of n-type pocket under the source enhances the ON current and OFF current of both the devices. L-shaped and U-shaped TFETs structure, both, are easy to fabricate and cost-effective due to the use of already established Si technology.

#### II. PROPOSED DEVICE STRUCTURE

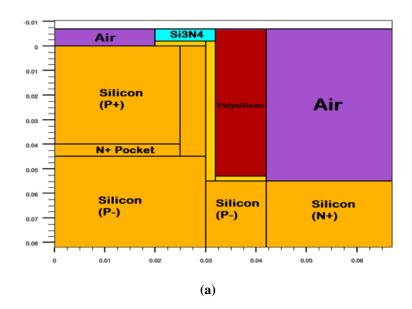

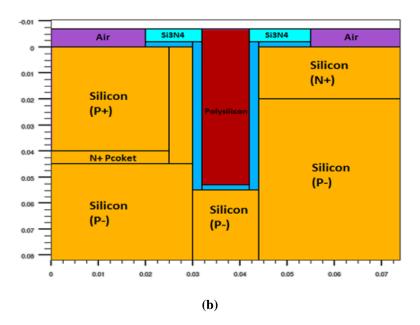

Figure 1 shows Si-based L-shaped and U-shaped TFETswithpolysilicon gate material of 14 nm gate length.

Page | 2885 Copyright © 2019Authors

Fig. 1. Schematic view of Si-source based (a) L-shaped TFET (b) U-shaped TFETfor different temperatures.

The source is considered as p-type and drain region is of n-type material, whereas the channel region is the intrinsic type of material. In TCAD simulations, the concentration used to dope source, pocket, drain, and channel are  $1x10^{21}$  cm<sup>-3</sup>,  $1x10^{19}$  cm<sup>-3</sup>,  $1x10^{19}$  cm<sup>-3</sup>, and  $1x10^{15}$  cm<sup>-3</sup>, respectively. The HfO<sub>2</sub> is used as the gate oxide material Si<sub>3</sub>N<sub>4</sub> is used as spacer material. The length of channel region, source region, and gate region are considered as 14 nm, 30nm, and 30 nm, respectively. The phonon-assisted BTBT generates the non-local generation rate of holes as well electrons which is represented by non-local BTBT model. The non-local BTBT model which is present in Atlas Silvaco TCAD is used for the device simulation.

#### III. SIMULATION RESULTS AND DISCUSSION

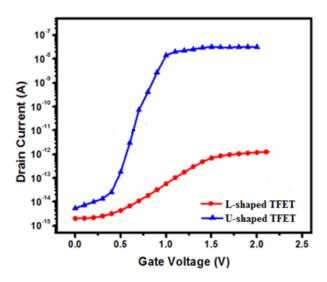

This section studies the behavior of both devices in terms of surface potential, electric field, and transfer characteristics. Comparison of Si-source based L-shaped TFET and U-shaped TFET is shown in Fig. 3. It is clear from the plot that U-shaped TFET shows better performance than the L-shaped TFET. The  $I_{ON}/I_{OFF}$  ratio of the U-shaped TFET is  $10^7$ . The drain voltage used for all the simulation study is  $V_{DS}$ = 0.8 V.

Page | 2886 Copyright @ 2019Authors

Fig. 2. Comparison of transfer characteristics of L-shaped TFET and U-shaped TFET.

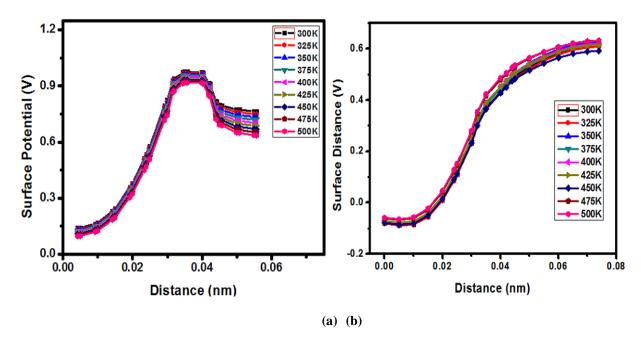

Fig. 3. Surface potential vs. distance of the channel of Si-source based (a) L shaped TFET (b) U shaped TFET for different temperature.

The surface potential vs. channel distance of L-shaped TFET is shown in Fig. 3(a). As the temperature varies from 300 k to 500 K, after channel distance 0.4 nm, the surface potential decreases with the increase of channel distance and due to which the drain current of the device also reduced, as shown in Fig. 2.Fig. 3(b) shows that the surface potential increase as the temperature increases from 300 K to 500 K and hence, increases the drain current of the device.

Page | 2887 Copyright @ 2019Authors

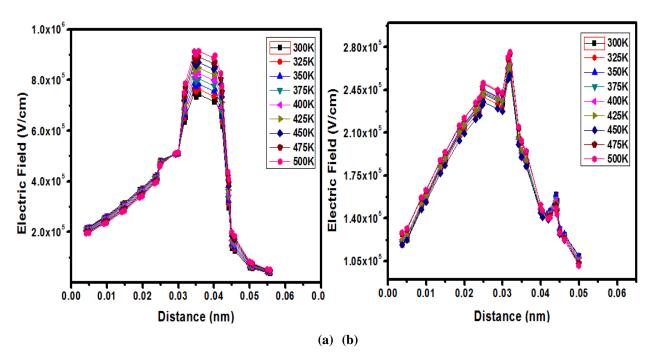

Fig. 4. Electric field vs. distance of the channel of Si-source based (a) L shaped TFET (b) U shaped TFETfor different temperature.

Fig. 4 shows the electric field vs. distance of the channel of Si based L shaped TFET and U shaped TFET for different temperatures. The peak of the electric field is large and sharp for U-shaped TFET and is smaller and not sharp for L-TFET.

Page | 2888 Copyright ⊚ 2019Authors

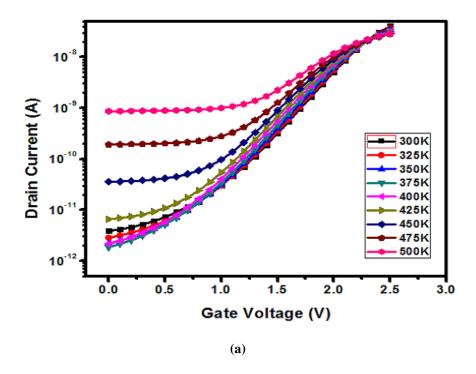

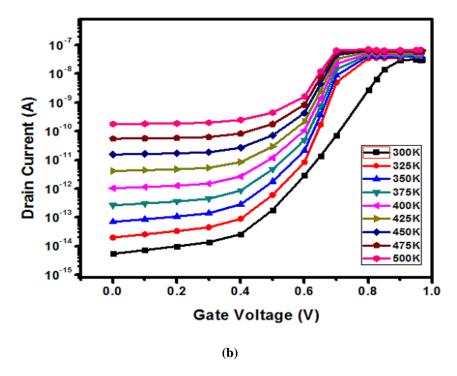

The drain current versus gate voltage variation is shown in Fig. 3. This figure is mainly focused on the OFF current of the both devices. In L-TFET, the OFF current is quite good for room temperature i.e., 300 K. But, as the temperature increases from 425 K, the leakage is more and the OFF current decreases without more the ON current, as shown in Fig. 5(a).

In U-TFET, the effect of temperature variation is less for drain current, as show in Fig 5 (b). As the temperature varies from 300 K to 500 K, the leakage current is lee in comparison to U-shaped TEFT.

Fig. 5. Drain current vs. gate voltage of Si-source based (a) L shaped TFET (b) U shaped TFET for different temperature.

## IV. CONCLUSION

In this paper, a comparative study of L-shaped Tunnel Field Effect Transistors (TFETs) and U-shaped TFETs have been done. The surface potential, electric field and transfer characteristics of both devices, i.e., L-shaped and U-shaped TFETs have been studied in terms oftemperature. The extension of physical channel length enhances the ON current as well as suppress the OFF current of L-shaped and U-shaped TFETs. Further improvement in U-shaped and L-shaped TFET has been done by adding n-type pocket under the source region. Both structures (L-shaped and

Page | 2889 Copyright @ 2019Authors

U-shaped TFETs), are easy to fabricate and cost-effective due to the use of already established Si technology. In next-generation devices, the superior performance of L-shaped and U-shaped TFETs structure makes them a promising contender for low power applications. The Atlas Silvaco TCAD software-based simulation results show that the U-shaped TFETs are superior to L-shaped TFETs.

#### References

- [1] A. M. Ionescu and H. Riel, "Tunnel field-effect transistors as energyefficient electronic switches," *Nature*, vol. 479, no. 7373, pp. 329–337,2011.

- [2] V. Nagavarapu, R. Jhaveri, and J. C. S. Woo, "The tunnel source (PNPN) n-MOSFET: A novel high performance transistor," *IEEE Trans. Electron Devices*, vol. 55, no. 4, pp. 1013–1019, 2008.

- P. Matheu, B. Ho, Z. A. Jacobson, and T.-J. K. Liu, "Planar GeOI TFET performance improvement with back biasing," *IEEE Trans. Electron Devices*, vol. 59, no. 6, pp. 1629–1635, 2012.

- [4] A. Villalon, G. Le Carval, S. Martinie, C. Le Royer, M.-A. Jaud, and S. Cristoloveanu, "Further insights in TFET operation," *IEEE Trans. Electron Devices*, vol. 61, no. 8, pp. 2893–2898, 2014.

- N. Gupta, A. Makosiej, A. Vladimirescu, A. Amara, and C. Anghel, "3T-TFET bitcell based TFET-CMOS hybrid SRAM design for ultralow power applications," *in Proc. Design, Autom. Test Eur. Conf. Exhibit.* (DATE), pp. 361–366, 2016.

- [6] K. Gopalakrishnan, P. B. Griffin, J. D. Plummer, "I-MOS: A novel semiconductor device with a subthreshold slope lower than \\$kT/q\\$", *IEDM Tech. Dig.*, pp. 289-292, 2002.

- [7] U. E. Avci, R. Rios, K. Kuhn, I. A. Young, "Comparison of performance switching energy and process variations for the TFET and MOSFET in logic", *Proc. Very Large Scale Integr. (VLSI) Technol. Symp.*, pp. 124-125, 2011.

- [8] W. Y. Choi, B.-G. Park, J. D. Lee, and T.-J. K. Liu, "Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec," *IEEE Electron Device Lett.*, vol. 28, no. 8, pp. 743–745, 2007.

- [9] D. B. Abdi, M. J. Kumar, "Controlling ambipolar current in tunneling FETs using overlapping gate-on-drain", *IEEE J. Electron Devices Soc.*, vol. 2, no. 6, pp. 187-190, 2014.

- [10] Z. Yang, "Tunnel field-effect transistor with an L-shaped gate," *IEEE Electron Device Lett.*, vol. 37, no. 7, pp. 839–842, 2016.

- [11] S. W. Kim, J. H. Kim, T.-J. King Liu, W. Y. Choi, and B.-G. Park, "Demonstration of L-shaped tunnel field-effect transistors," *IEEE Trans. Electron Devices*, vol. 63, no. 4, pp. 1774–1778, 2016.

- [12] W. Wang, P.-F. Wang, C.-M. Zhang, X. Lin, X.-Y. Liu, Q. Q. Sun, P. Zhou, and D. W. Zhang, "Design of U-shape channel tunnel FETs with SiGe source regions," *IEEE Trans. Electron Devices*, vol. 61, no. 1, pp. 193–197, 2014.

- [13] K. Boucart, A. M. Ionescu, "Double-gate tunnel FET with high-k gate dielectric", *IEEE Trans. Electron Devices*, vol. 54, no. 7, pp. 1725-1733, 2007.

- [14] S. H. Kim, H. Kam, C. Hu, T.-J. K. Liu, "Germanium-source tunnel field effect transistors with with record high I<sub>ON</sub>/I<sub>OFF</sub>, *VLSI Symp. Tech. Dig.*, pp. 178-179, 2009.

- [15] C. Anghel, G. Hraziia, A. Gupta, A. Amara, A. Vladimirescu, "30-nm tunnel FET with improved performance and reduced ambipolar current", *IEEE Trans. Electron Devices*, vol. 58, no. 6, pp. 1649-1654, 2011.

Page | 2890 Copyright © 2019Authors

# THINK INDIA JOURNAL

ISSN: 0971-1260 Vol-22-Issue-17-September-2019

- [16] K. K. Bhuwalka, J. Schulze, I. Eisele, "Performance enhancement of vertical tunnel field-effect transistor with SiGe in the δp+ layer", *Jpn. J. Appl. Phys.*, vol. 43, pp. 4073-4078, 2004.

- [17] V. Nagavarapu, R. Jhaveri, J. C. S. Woo, "The tunnel source (PNPN) n-MOSFET: A novel high performance transistor", *IEEE Trans. Electron Devices*, vol. 55, no. 4, pp. 1013-1019, 2008.

- [18] S. W. Kim, W. Y. Choi, M.-C. Sun, H. W. Kim, B.-G. Park, "Design guideline of Si-based L-shaped tunneling field-effect transistors", *Jpn. J. Appl. Phys.*, vol. 51, no. 6S, pp. 06FE09-1-06FE09-4, 2012.

- [19] S. W. Kim, W. Y. Choi, M.-C. Sun, B.-G. Park, "Investigation on the corner effect of L-shaped tunneling field-effect transistors and their fabrication method", *J. Nanosci. Nanotechnol.*, vol. 13, no. 9, pp. 6376-6381, 2013.

- [20] W. Wang, P.-F. Wang, C.-M. Zhang, X. Lin, X.-Y. Liu, Q. Q. Sun, P. Zhou, and D. W. Zhang, "Design of U-shape channel tunnel FETs with SiGe source regions," *IEEE Trans. Electron Devices*, vol. 61, no. 1, pp. 193–197, 2014.

Page | 2891 Copyright @ 2019Authors